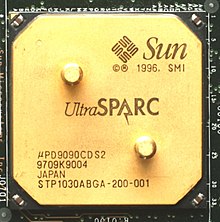

UltraSPARC

L’UltraSPARC est un micro-processeur développé par Sun Microsystems et fabriqué par Texas Instruments. Il implémente le jeu d'instructions SPARC V9. Il a été mis sur le marché en 1995. Il fut le premier micro-processeur de Sun Microsystems qui implémenta ce jeu d'instructions. Marc Tremblay participa à sa création.

| Production | De 1995 à 1997 |

|---|---|

| Fabricant | Texas Instruments |

| Fréquence | 143 MHz à 200 MHz |

|---|

| Cœur | double UAL |

|---|---|

| Boîtier | matrice de billes 521 broches |

| Architecture | SPARC V9 64 bits |

|---|---|

| Boutisme | gros-boutiste |

Microarchitecture

modifierL'UltraSPARC est un micro-processeur superscalaire capable de gérer ses instructions dans le désordre (Exécution out-of-order). Il est en mesure de traiter quatre instructions en parallèle. Il possède un pipeline d'exécution d'une profondeur de 8 étages.

Unité fonctionnelle

modifierL'unité d'exécution a été simplifiée comparé au SuperSPARC pour obtenir de plus grande fréquence. Un exemple de simplification est l'unité arithmétique et logique (UAL) qui n'a pas été connectée en cascade comme ce fut le cas sur le SuperSPARC.

Le micro-processeur possède 32 registres 64 bits. Combiné avec ses fenêtres de registres (l'UltraSPARC en possède 8), le processeur arrive à un total de 144 registres. Le processeur possède également sept registres d'entrée et 3 registres de sortie. Les registres donnent également accès à deux unités arithmétiques et logiques ainsi que l'unité d'accès à la mémoire. Les deux UALs sont en mesure de faire des opérations d'arithmétique, de logique et de décalages de bits. Une restriction étant qu'une seule des deux UALs peut faire les opérations de multiplication et division.

Ce processeur possède également une unité de calcul à virgule flottante découpées en cinq parties :

- une unité pour la gestion des additions et soustractions ;

- une pour les multiplications ;

- une pour les divisions et les racines carrées ;

- deux unités pour l'exécution des instructions SIMD définie par le Visual Instruction Set (VIS). Le tableau de registre pour les opérations en virgules flottantes sont au nombre de 32 registres de 64 bits. Cinq sont consacrés aux ports d'entrées et trois aux ports de sortie.

Cache

modifierL'UltraSPARC a deux niveaux de cache : primaire et secondaire. Le primaire est lui-même constitué de deux parties : un cache pour les instructions, un autre pour les données. Les deux ont une capacité de 16 Ko.

L'UltraSPARC nécessite également l'utilisation d'un cache secondaire externe. Ce cache est unifié et peut avoir une capacité comprise en 512 ko et 4 Mo et est de type direct-mapped. Les données en cache sont accessibles en un seul cycle. Le cache externe se compose de mémoire SRAM synchrone cadencé à la même vitesse que le micro-processeur (l'utilisation d'un ratio multiplicateur n'est pas supporté). Il est accessible via le bus de données.

Fabrication

modifierIl est composé de 3,8 millions de transistors. Il fut fabriqué à l'aide du procédé CMOS EPIC-3 de Texas Instrument avec une finesse de gravure de 0,5 µm et 4 niveaux de métal. L'UltraSPARC ne fut pas fabriqué à l'aide de procédé BiCMOS car selon Texas Instruments, le procédé ne s'appliquait pas bien en gravure 0,5 µm et n'offrait que peu d'avantage en matière de performances. Le procédé fut d'abord perfectionné sur le TI MVP (processeur de signal numérique ou DSP) avec une spécification revue à la baisse notamment au niveau du nombre de couches de métal (3 niveaux au lieu de 4) et une finesse de gravure de 0,55 µm, avant d'être appliqué à l'UltraSPARC pour éviter de répéter les erreurs qui avaient été rencontrées avec le SuperSPARC.

Conditionnement

modifierL'UltraSPARC se présente sous la forme d'une matrice de billes en plastique (PBGA en anglais) et est constituée de 521 contacteurs.

Références

modifier- Greenley, D. et al. (1995). "UltraSPARC: The next generation superscalar 64-bit SPARC". Proceedings of Compcon '95: p. 442–451.

- Gwennap, Linley (3 October 1994). "UltraSparc Unleashes SPARC Performance". Microprocessor Report, Volume 8, Number 13.

- Gwennap, Linley (5 December 1994). "UltraSparc Adds Multimedia Instructions". Microprocessor Report.