Serial Peripheral Interface

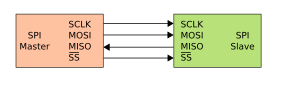

Une liaison SPI (pour Serial Peripheral Interface) est un bus de données série synchrone baptisé ainsi par Motorola, au milieu des années 1980 qui opère en mode full-duplex. Les circuits communiquent selon un schéma maître-esclave, où le maître contrôle la communication. Plusieurs esclaves peuvent coexister sur un même bus, dans ce cas, la sélection du destinataire se fait par une ligne dédiée entre le maître et l'esclave appelée « Slave Select (SS) ».

Interface

modifierLe bus SPI utilise quatre signaux logiques :

- SCLK — Serial Clock, Horloge (généré par le maître)

- MOSI — Master Output, Slave Input (généré par le maître)

- MISO — Master Input, Slave Output (généré par l'esclave)

- SS — Slave Select, Actif à l'état bas (généré par le maître)

Il existe d'autres noms qui sont souvent utilisés :

- SCK, SCL — Horloge (généré par le maître)

- SDO, SDA, DO, SO — Serial Data OUT, MOSI

- SDI, DI, SI — Serial Data IN, MISO

- nCS, CS, nSS, STE, CSN— SS

Dans le cas de la convention de nommage SDI/SDO, le SDO du maître doit être relié au SDI de l'esclave et vice versa. Pour éviter les confusions au moment du câblage, il est donc souvent recommandé d'utiliser les dénominations MISO-MOSI qui évitent une certaine ambiguïté ; pour exemple, une librairie graphique[1] écrite par Adafruit, prend en charge plusieurs références de contrôleurs d'écrans qui, malgré leurs actions similaires, ne possède pas toujours les mêmes noms de broches. Afin d'éviter ce "problème" les développeurs ont renommé les broches MISO/MOSI par RD et WR signifiant respectivement ReaD (lire) et WRite (écrire) ; en conclusion, on se demande si la broche Lire permet au Microcontroleur de Lire le Module LCD ou alors si elle permet au Module de Lire et donc au Microcontroleur de lui Écrire une donnée ?

Fonctionnement

modifierUne transmission SPI typique est une communication simultanée entre un maître et un esclave :

- Le maître génère l'horloge et sélectionne l'esclave avec qui il veut communiquer par l'utilisation du signal SS

- L'esclave répond aux requêtes du maître

À chaque coup d'horloge le maître et l'esclave s'échangent un bit. Après huit coups d'horloges le maître a transmis un octet à l'esclave et vice versa. La vitesse de l'horloge est réglée selon des caractéristiques propres aux périphériques.

Polarité et phase de l'horloge

modifierLa configuration de la SPI est souvent nommée dans les documentations techniques sous forme de nombre ou de couple, où le bit de poids fort est CPOL (Clock Polarity) et le bit de poids faible CPHA (Clock Phase)

| Mode | CPOL | CPHA |

|---|---|---|

| 0 (0,0) | 0 | 0 |

| 1 (0,1) | 0 | 1 |

| 2 (1,0) | 1 | 0 |

| 3 (1,1) | 1 | 1 |

Les modes 0 et 3 sont identiques en transmission, seul change l'état de la ligne d'horloge au repos. C'est pour cette raison que de nombreux périphériques peuvent être capables de dialoguer soit en mode 0 et 3, soit en mode 1 et 2.

Avantages et Inconvénients

modifierAvantages

modifier- Communication Full duplex

- Débit plus important qu'un bus I2C

- Flexibilité du nombre de bits à transmettre ainsi que du protocole en lui-même

- Simplicité de l'interface matérielle

- Aucun arbitre nécessaire car aucune collision possible

- Les esclaves utilisent l'horloge du maître et n'ont donc pas besoin d'oscillateur propre

- Pas de phy nécessaire

- Partage d'un bus commun pour l'horloge, MISO et MOSI entre les périphériques

Inconvénients

modifier- Monopolise plus de broches d'un boîtier que l'I2C ou une UART qui en utilisent seulement deux.

- Aucun adressage possible, il faut une ligne de sélection par esclave en mode non chaîné.

- Le protocole n'a pas d'acquittement. Le maître peut parler dans le vide sans le savoir.

- La plupart des implémentations ne tolèrent la présence que d'un seul maître SPI sur le bus. Néanmoins, on trouve des circuits intégrés supportant le mode « multi-master », permettant de partager le bus SPI entre plusieurs maîtres. Les implémentations pratiques de ce genre restent rares.

- Ne s'utilise que sur de courtes distances contrairement aux liaisons RS-232, RS-485 ou bus CAN. Néanmoins, il est possible d'utiliser des tampons de bus, comme des adaptateurs RS-232 (exemple : MAX208, MAX3110E ou MAX3111E de TI), RS-485 ou LVDS pour relier un maître et un esclave avec un câble de quelques mètres. La mise en œuvre de ces circuits reste délicate car il devient nécessaire de procéder à des adaptations d'impédance pour éviter les oscillations parasites (en).

Outils de développement

modifierIl existe une grande variété d'instruments contrôlés par PC permettant d'agir comme maître et/ou analyseur de protocole SPI. Ces outils peuvent parfois être utilisés pour des protocoles série dérivant du protocole SPI, comme les protocoles sur 3 fils.

Analyseurs de protocole SPI

modifierUn analyseur de protocole SPI est un outil échantillonnant un bus SPI et décodant les signaux numériques pour fournir un décodage haut niveau des transactions SPI. Ces analyseurs sont des instruments indépendants ou sont fournis comme extensions à certains modèles d'oscilloscope.

Notes et références

modifier- Adafruit library for 8-bit TFT LCDs such as ILI9325, ILI9328, etc, Adafruit Industries, (lire en ligne)

Voir aussi

modifierArticles connexes

modifierLiens externes

modifier« SPI Signal Names - SparkFun Electronics », sur www.sparkfun.com (consulté le )