Module multipuce

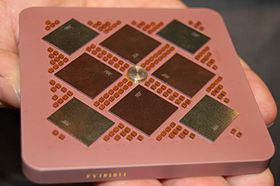

Un module multipuce (en anglais : Multi-chip module ou MCM) est un assemblage électronique (tel qu’un boîtier équipé d'un certain nombre de bornes conductrices ou « broches ») dans lequel plusieurs circuits intégrés (CI ou « puces »), puces de semi-conducteur et/ou d’autres composants discrets sont intégrés, généralement sur un substrat unificateur, de sorte qu’à l’usage, il peut être traité comme s’il s’agissait d’un seul circuit intégré plus grand[1]. D’autres termes pour désigner un boîtier MCM incluent « intégration hétérogène » ou « circuit intégré hybride (en) »[2]. L’avantage de l’utilisation du boîtier MCM est qu’il permet à un fabricant d’utiliser plusieurs composants pour la modularité et/ou pour améliorer les rendements de fabrication par rapport à une approche conventionnelle de circuits intégrés monolithiques.

Un module multipuce Flip Chip (Flip Chip Multi-Chip Module, FCMCM) est un module multipuce qui utilise la technologie Flip Chip. Un FCMCM peut comporter une grande puce et plusieurs puces plus petites, le tout sur le même module[3].

Description

modifierLes modules multi-puces se présentent sous différentes formes en fonction de la complexité et des philosophies de développement de leurs concepteurs. Celles-ci peuvent aller de l’utilisation de circuits intégrés regroupés sur un petit circuit imprimé (PCB) destiné à imiter l’empreinte d’un boîtier existant à des boîtiers entièrement personnalisés intégrant de nombreuses puces sur un substrat d’interconnexion haute densité (HDI).

Le substrat du MCM assemblé final peut être réalisé de l’une des manières suivantes :

- le substrat est un circuit imprimé (PCB) laminé multicouche, comme celui utilisé dans les processeurs Zen 2 d’AMD ;

- le substrat est construit sur de la céramique, telle que la céramique cocuite (en) à basse température ;

- les circuits intégrés sont déposés sur le substrat de base à l’aide de la technologie couche mince.

Les circuits intégrés qui composent le boîtier MCM peuvent être :

- des circuits intégrés capables d’exécuter la plupart, sinon la totalité, des fonctions d’un composant d’un ordinateur, tel que le processeur. Les implémentations de POWER5 d’IBM et du Core 2 Quad d’Intel en sont des exemples. Plusieurs copies du même circuit intégré sont utilisées pour construire le produit final. Dans le cas de POWER5, plusieurs processeurs POWER5 et leur cache L3 hors puce associé sont utilisés pour construire le boîtier final. Avec le Core 2 Quad, deux puces Core 2 Duo ont été encapsulées ensemble.

- des circuits intégrés qui n’exécutent que certaines des fonctions, ou « blocs de propriété intellectuelle » (« blocs IP »), d’un composant d’un ordinateur. Ceux-ci sont connus sous le nom de chiplets (en)[4],[5]. Un exemple de ceci sont les circuits de traitement (CPU) et les circuits d’E/S des processeurs Zen 2 d’AMD.

Un interposeur (en) relie les circuits intégrés. Celui-ci est souvent organique (un circuit imprimé qui contient du carbone, et est donc organique) ou est fait de silicium (comme dans les High Bandwidth Memory)[6]. Chacune de ces solutions a des avantages et des limites. L’utilisation d’interposeurs pour connecter plusieurs circuits intégrés au lieu de connecter plusieurs circuits intégrés monolithiques dans des boîtiers séparés réduit la puissance nécessaire pour transmettre des signaux entre les circuits intégrés, augmente le nombre de canaux de transmission et réduit les retards causés par la résistance et la capacité (retards RC)[7]. Cependant, la communication entre les chiplets consomme plus d’énergie et a une latence plus élevée que les composants des circuits intégrés monolithiques[8].

MCM pile de puces

modifierUn développement relativement nouveau dans la technologie MCM est le boîtier dit « pile de puces »[9]. Certains circuits intégrés, en particulier les mémoires, ont des brochages très similaires ou identiques lorsqu’ils sont utilisés plusieurs fois dans les systèmes. Un substrat soigneusement conçu peut permettre à ces puces d’être empilées dans une configuration verticale, ce qui réduit considérablement l’empreinte du MCM résultant (bien qu’au prix d’une puce plus épaisse ou plus haute). Étant donné que la surface est plus souvent limitée dans les conceptions électroniques miniatures, la pile de puces est une option attrayante dans de nombreuses applications telles que les téléphones portables et les assistants numériques personnels (PDA). Grâce à l’utilisation d’un circuit intégré 3D (en) et d’un procédé d’amincissement, jusqu’à dix puces peuvent être empilées pour créer une carte mémoire SD de grande capacité[10]. Cette technique peut également être utilisée pour la High Bandwidth Memory (mémoire à bande passante élevée).

Un moyen possible d’augmenter les performances du transfert de données dans la pile de puces est d’utiliser des réseaux sans fil sur puce (WiNoC)[11].

Références

modifier- (en) Rao Tummala, Solid State Technology, « SoC vs. MCM vs SiP vs. SoP » (consulté le ).

- (en) Don Scansen, « Chiplets: A Short History] », EE Times (consulté le )

- (en) « IMAPS Advancing Microelectronics 2020 Issue 3 (Advanced SiP) », sur FlippingBook (consulté le )

- (en) Samuel K. Moore, « Intel's View of the Chiplet Revolution », IEEE Spectrum (consulté le )

- (en) « Chiplets », Semi Engineering (consulté le )

- (en) « 2.5D - Semiconductor Engineering », sur Semiengineering.com (consulté le )

- (en) « Interposers », sur Semiengineering.com (consulté le )

- (en-US) Dr. Ian Cutress, « Intel Moving to Chiplets: 'Client 2.0' for 7nm », AnandTech (consulté le )

- (en) Jon Worrel, « Intel migrates to desktop Multi-Chip Modules (MCMs) with 14nm Broadwell », Fudzilla, (consulté le )

- (en) Richard Chirgwin, « Memory vendors pile on '3D' stacking standard », The Register, (consulté le ).

- (en) Slyusar V. I. et Slyusar D.V. « Pyramidal design of nanoantennas array. » (lire en ligne) [PDF]

—VIII International Conference on Antenna Theory and Techniques (ICATT’11) (Kyiv, Ukraine - National Technical University of Ukraine “Kyiv Polytechnic Institute”, 20-23 septembre 2011)