Intégrité du signal

En électronique logique et numérique, l'expression intégrité du signal ou SI (pour signal integrity en anglais) désigne la qualité du signal électrique qu'il est nécessaire de maintenir pour que le système effectue la tâche pour laquelle il est conçu[1].

Le souci de l'intégrité du signal surgit dans la conception d'un nouveau dispositif électronique au moment de passer du schéma de principe au dessin de sa réalisation matérielle. Aux cadences supérieures à 100 MHz (Bogatin 2009, p. 3), on ne peut plus négliger, comme dans le schéma, les caractéristiques électriques des connexions entre composants : une simple conducteur a une résistance et une réactance, et dans leur réseau serré, chacun interfère au moins avec les plus proches. Le schéma de principe ne représente pas, en général, l'alimentation des circuits ; celle-ci peut cependant, en faisant varier les tensions de référence, affecter le signal.

Dans les conducteurs, le signal électrique se propage à environ la moitié de la vitesse de la lumière, ce qui ramené à la taille d'un circuit donne 15 cm/ns : aux cadences élevées, le temps que met le signal pour passer d'un composant à un autre n'est pas négligeable. Le rapport entre le temps de propagation entre deux éléments et la période du renouvellement du signal logique est un indicateur important de la nature des problèmes attendus.

L'intégrité du signal est ensuite une exigence dans l'intégration des systèmes électroniques et dans leur exploitation.

Généralités

modifierEn électronique logique, qu'elle soit numérique ou partie d'un automatisme, les signaux peuvent avoir exclusivement deux valeurs, 0 ou 1, à un instant donné. Le signal électrique qui doit représenter ces valeurs est une grandeur — le plus souvent, la tension — qui varie sur une échelle continue. Le circuit récepteur convertit, à un certain moment, la valeur électrique moyenne de ce signal sur une certaine durée, en une valeur logique. Au cours de la transmission du signal électrique, le bruit de fond des circuits, les interférences, la distorsion linéaire ou non, des pertes, des retards et autres effets indésirables affectent les signaux électriques.

On parle d'intégrité du signal lorsque le signal électrique, malgré les perturbations, correspond sans erreur au signal logique.

Sur de courtes distances, à faible cadence, et assez loin d'une autre ligne parallèle, un simple conducteur peut transmettre un signal logique avec une fidélité suffisante. À un débit binaire élevé, sur de plus longues distances ou à travers des milieux divers, plusieurs effets peuvent dégrader le signal électrique au point de causer des erreurs fatales[a] et des pannes dans le système ou le dispositif. L'ingénierie de l'intégrité du signal consiste à analyser et à atténuer ces effets. Cette activité est cruciale pour la conception et l'assemblage des composants électroniques, des connexions internes d'un circuit intégré (IC)[2] à ses liaisons au boîtier, pour les cartes de circuit imprimé (PCB), le fond de panier et les connexions inter-équipements[3]. Bien que des thèmes communs relient ces différents niveaux, des considérations pratiques entraînent des différences substantielles entre ces applications. Le rapport entre temps de propagation dans les conducteurs concernés et cadence de succession des bits est un indice de difficultés particulières.

La distorsion, la suroscillation, la diaphonie, le rebond de masse (en)[b], les réflexions en bout de ligne, les interférences, la perte de signal et le bruit d'alimentation affectent l'intégrité du signal.

L'intégration des systèmes électroniques dans une installation industrielle affecte l'intégrité du signal, dès lors que les protocoles de transmission impliquent des débits importants, comme avec des liaisons directes sur fibre optique entre sous-ensembles. L'intégrité du signal implique le respect d'un certain nombre de pratiques, qui se retrouvent au cours de l'exploitation de l'installation, dans la mesure où celle-ci peut entraîner des modifications, volontaires ou non[4].

Historique

modifierL'intégrité du signal concerne principalement les performances électriques des fils et des autres supports de transmission qui transportent les signaux dans un dispositif électronique ou entre 2 équipements. Les questions de performance relèvent de la physique de base et sont ainsi restées relativement inchangées depuis le début de la signalisation électronique logique. Le premier câble télégraphique transatlantique a souffert de graves problèmes d'intégrité du signal. L'analyse de ces problèmes a produit beaucoup des nombreux outils mathématiques qui servent encore de nos jours pour analyser les problèmes d'intégrité du signal, comme les équations des télégraphistes. Vers 1940, des systèmes comme le commutateur téléphonique Western Electric, basé sur des relais métalliques à ressort, subissaient presque tous les effets perturbant les produits numériques modernes : oscillations, diaphonie, le rebond[c] et le bruit d'alimentation. En 1948, Claude Shannon fonde sa théorie de l'information sur la question de l'intégrité de l'information dans un signal électrique en présence de bruit et de distorsion[5].

Sur les circuits imprimés, on a commencé à se préoccuper sérieusement de l'intégrité du signal lorsque les temps de transition des signaux (montée et descente) sont devenus comparables au temps de propagation à travers la carte, à peu près quand les cadences excèdent quelques dizaines de MHz. Initialement, seuls les signaux les plus importants ou les plus rapides nécessitaient une analyse ou une conception détaillée. À mesure que les vitesses augmentaient, les méthodes d'analyse de l'intégrité du signal et les pratiques associées ont concerné une part de plus en plus grande des signaux. Dans les circuits modernes, à plus de 100 MHz, il faut étudier pratiquement tout.

Pour les circuits intégrés, la miniaturisation des règles de gravure a rendu l'analyse SI nécessaire. Au début de l'ère VLSI moderne, la conception et la disposition des circuits à puce numérique étaient des procédés manuels. L'utilisation de l'abstraction et l'application de techniques de synthèse automatique ont permis aux concepteurs d'utiliser des langages de haut niveau et d'appliquer un processus de conception automatisé pour mettre au point des organisations très complexes, ignorant dans une large mesure les caractéristiques électriques des circuits sous-jacents. La tendance de doublement périodique de la complexité du matériel informatique (loi de Moore) a ramené les effets électriques à l'avant-plan dans les systèmes technologiques récents. Avec le réduction de la résolution de gravure en dessous de 0,25 µm, les délais de transmission sont devenus au moins aussi importants que les délais des portes logiques. Il a fallu en tenir compte pour garantir le respect des temps de synchronisation. Pour les nanotechnologies de 0,13 µm et moins, les interactions involontaires entre les signaux, comme la diaphonie, sont devenues une considération importante dans la conception numérique. Pour ces technologies, on ne peut pas assurer les performances et l'exactitude d'une conception sans tenir compte des effets du bruit.

La suite de cet article concerne principalement l'intégrité du signal dans les technologies électroniques modernes. Toutefois, les principes de l'intégrité du signal ne sont pas limités aux technologie actuelles. L'intégrité du signal existait bien avant et continuera tant que les communications électroniques existeront.

Intégrité des signaux internes à une puce

modifierLes problèmes d'intégrité du signal dans les circuits intégrés (CI) modernes peuvent entraîner des conséquences sévères dans les équipements numériques :

- les produits peuvent ne pas fonctionner du tout, ou pire, devenir peu fiables sur le terrain;

- la conception peut fonctionner, mais uniquement à des vitesses plus lentes que prévu;

- le rendement peut diminuer, parfois de façon drastique.

Ces défaillances sont très coûteuses. Les coûts encourus comprennent les coûts des masques photoélectriques, les coûts d'ingénierie et les coûts d'opportunité causés par une introduction retardée du produit. Par conséquent, on a développé des outils d'automatisation de la conception électronique pour analyser, prévenir et corriger ces problèmes[2]. Dans les circuits intégrés (CI), la diaphonie est la principale cause des problèmes d'intégrité du signal. Dans les technologies CMOS, elle est principalement causée par la capacité de couplage. Cependant, en général, elle peut être causée entre autres par une inductance mutuelle, un couplage de substrat et un fonctionnement de porte non idéal. Les correctifs impliquent normalement de changer la taille des amplificateurs, l'espacement des fils ou les deux.

Dans les circuits analogiques, les concepteurs se préoccupent également du bruit provenant de sources physiques, comme le bruit thermique, le bruit de scintillement et le bruit de grenaille. Ces sources de bruit constituent d'une part une limite inférieure au plus petit signal qu'on peut amplifier, et d'autre part, une limite supérieure à l'amplification utile.

Dans les circuits intégrés numériques, le bruit dans un signal provient surtout des effets de couplage causés par la commutation d'autres signaux. L'augmentation de la densité d'interconnexion a rapproché physiquement chaque fil de ses voisins, produisant une diaphonie accrue entre des signaux voisins. Les dimensions des circuits ayant diminué conformément à la loi de Moore, plusieurs causes ont aggravé les problèmes de bruit. Les principales sont les suivantes.

- Pour conserver une résistance acceptable malgré une largeur réduite, les géométries des fils modernes sont plus épaisses proportionnellement à leur espacement. Cela augmente les capacités parasites vis-à-vis des signaux latéraux, au détriment de la capacité par rapport à la terre (GND), augmentant ainsi les tensions de bruit induites (exprimées en fraction de la tension d'alimentation).

- La mise à l'échelle de la technologie a entraîné une baisse des tensions de seuil pour les transistors MOS et a également réduit la différence entre les tensions de seuil et d'alimentation, réduisant ainsi l'immunité au bruit (en)[d].

- Les vitesses des signaux logiques, et les vitesses d'horloge en particulier, ont augmenté de manière significative, conduisant ainsi à des temps de transition (montée et descente) plus rapides. Ces temps de transition plus rapides sont étroitement liés à une diaphonie capacitive plus élevée. De plus, à de telles vitesses, les propriétés inductives des fils entrent en jeu, surtout l'inductance mutuelle.

Ces causes ont augmenté les interactions entre les signaux et diminué l'immunité au bruit des circuits CMOS numériques. Ils ont fait du bruit un problème important pour les circuits intégrés numériques qui doit être pris en compte par les concepteurs de puces numériques avant le lancement de la fabrication de la puce. Plusieurs problèmes doivent être minimisés.

- Le bruit peut faire prendre au signal la mauvaise valeur. Ceci est particulièrement critique lorsqu'on est sur le point de verrouiller ou échantillonner le signal, car une valeur incorrecte pourrait être chargée dans un élément de stockage, provoquant une défaillance logique.

- Le bruit peut retarder la stabilisation du signal à la valeur correcte. Ce phénomène est souvent appelé bruit sur retard.

- Le bruit (par exemple, une suroscillation) peut faire chuter la tension d'entrée d'une porte en dessous du niveau de la masse (0 V) ou lui faire dépasser la tension d'alimentation. Cela peut réduire la durée de vie de l'appareil en sollicitant les composants, en induisant un état de verrouillage (en)[e] à l'état passant[f] ou en provoquant des changements d'état multiples de signaux qui ne devraient changer d'état qu'une seule fois au cours d'une période donnée.

Recherche des problèmes d'intégrité du signal dans les circuits intégrés

modifierEn règle générale, un concepteur de circuits intégrés doit prendre les mesures suivantes pour la vérification de l'intégrité du signal.

- Relever le schéma de la configuration en figurant les réactances et les liaisons capacitives et inductives parasites. On prend généralement les valeurs correspondant au meilleur et au pire cas pour les utiliser dans les simulations. Pour les circuits intégrés, contrairement aux circuits imprimés, on n'effectue presque jamais la mesure physique des grandeurs électriques, car les mesures in situ à l'aide d'équipement externe sont extrêmement difficiles. En outre, toute mesure aurait lieu après la création de la puce, trop tard pour résoudre les problèmes observés.

- Créer une liste des événements de bruit attendus pour les différents types de bruits, tels que le couplage et le partage de charges (en).

- Créer un modèle pour chaque événement de bruit. Il est essentiel que le modèle soit aussi précis que nécessaire pour modéliser l'événement de bruit donné.

- Pour chaque événement de signal, décider comment exciter le circuit afin que l'événement de bruit se produise.

- Créer un netlist SPICE (ou autre simulateur de circuit) représentant l'excitation souhaitée, afin d'inclure autant de scénarios que nécessaire. Les scénarios peuvent simuler des inductances et capacités parasites, ainsi que plusieurs effets de distorsion.

- Exécuter des simulations SPICE. Analyser les résultats de la simulation pour décider si une nouvelle conception est nécessaire. On analyse couramment les résultats avec un diagramme de l'œil et en calculant un budget de synchronisation[6].

Les outils modernes d'intégrité du signal utilisés dans la conception de circuits intégrés exécutent toutes ces étapes automatiquement, produisant des rapports qui donnent à une conception le feu vert ou une liste de problèmes à résoudre. Cependant, on n'applique généralement pas de tels outils sur l'ensemble d'un CI, mais uniquement sur des signaux d'intérêt sélectionnés.

Résolution des problèmes d'intégrité du signal dans les circuits intégrés

modifierUne fois un problème détecté, on doit le corriger. Voici quelques correctifs typiques pour les problèmes de puce des circuits intégrés.

- Suppression des discontinuités d'impédance. Trouver des endroits où les désadaptations d'impédance sont importants et ajuster la géométrie du chemin dans le but d'adapter l'impédance de façon qu'elle corresponde mieux au reste de la trace.

- Optimisation des amplificateurs. Il est possible d'avoir trop d'amplification ou pas assez.

- Insertion d'un répéteur. Dans cette approche, plutôt que d'augmenter la taille de l'amplificateur concerné, on insère un répéteur à un endroit approprié dans le réseau affecté.

- Réduction des agresseurs. On augmente les temps de transition (montée et descente) du signal agresseur en réduisant la force de son amplificateur.

- Ajout d'un blindage. Ajouter un blindage sur les réseaux critiques ou sur les réseaux d'horloge à l'aide de blindages GND ou VDD dans le but de réduire les effets de la diaphonie. Cette technique peut conduire à une longueur de routage excessive.

- Modifications du routage. Les changements de routage peuvent être très efficaces pour résoudre les problèmes de bruit, principalement en utilisant l'éloignement de signaux critiques pour réduire les effets de couplage les plus gênants.

Ces correctifs peuvent entraîner d'autres problèmes. Ces problèmes doivent être traités dans le cadre des flots de conception et de la fin de la conception. Il est prudent d'effectuer une nouvelle analyse après des modifications de conception.

Intégrité du signal puce à puce

modifierDans le cas des connexions câblées, il est important de comparer le temps de propagation de l'interconnexion à la période binaire pour décider quel type de connexion est nécessaire entre celles à impédance adaptée et celles sans adaptation.

Le temps de propagation du canal (retard) de l'interconnexion est d'environ 1 ns par 15 cm de FR-4 à trois plans (stripline (en)). La vitesse de propagation dépend du diélectrique et la géométrie[7]. Les réflexions des impulsions précédentes, dues aux désadaptations d'impédance, disparaissent après quelques rebonds d'un bout à l'autre de la ligne, c'est-à-dire sur une échelle de temps de l'ordre du temps de propagation. À faible débit binaire, les échos disparaissent d'eux-mêmes et, à mi-parcours, ne sont plus une préoccupation. L'adaptation d'impédance n'est ni nécessaire, ni souhaitable. De nombreux types de cartes de circuits imprimés autres que FR-4 existent, mais leur fabrication est généralement plus coûteuse.

La tendance vers des débits plus élevés s'est accélérée de façon spectaculaire en 2004 avec l'introduction de la norme PCI Express par Intel. À sa suite, la majorité des normes de connexion puce à puce ont subi une transition architecturale des bus parallèles vers des liaisons par sérialiseur/désérialiseur (en) nommées « chenal[g] ». Ces liaisons série éliminent le décalage d'horloge des bus parallèles et réduisent le nombre de traces et les effets de couplage résultants. Cependant, ces avantages se traduisent par une augmentation importante du débit binaire sur les voies et des périodes binaires plus courtes.

À des débits de données de plusieurs gigabits/s, les concepteurs de liaisons doivent tenir compte des réflexions dues aux changements d'impédance (comme lorsque les traces changent de niveau en passant dans les vias), du bruit induit par des connexions voisines densément tassées (diaphonie) et de l'atténuation des hautes fréquences que causent l'effet de peau dans la bande de métal et l'angle de perte diélectrique. Parmi les techniques d'atténuation de ces dégradations, on trouve une refonte du dessin des vias pour assurer l'adaptation des impédances, l'utilisation de la signalisation différentielle et la préaccentuation du signal à l'émission[8],[9].

À ces débits de plusieurs gigabits/s, la période binaire est plus courte que le temps de propagation. Des échos d'impulsions précédentes peuvent arriver au récepteur superposés à l'impulsion principale et la corrompre. En ingénierie des communications, on appelle ce phénomène l'interférence inter-symbole. Dans l'ingénierie d'intégrité du signal, on l'appelle généralement fermeture en forme d'œil (en référence au diagramme dit de l'œil rencontré au centre d'un type de trace d'oscilloscope). Lorsque la période binaire est plus courte que le temps de vol, il est crucial d'éliminer les réflexions en utilisant des techniques micro-ondes classiques comme l'adaptation d'impédances de l'émetteur à l'interconnexion, l'adaptation des sections d'interconnexion entre elles et enfin l'adaptation de l'interconnexion au récepteur. L'impédance d'interconnexion possible est contrainte par l'impédance de l'espace libre ≈(377 Ω), par un facteur de forme géométrique et par la racine carrée de la constante diélectrique relative de la garniture de la stripline (généralement FR-4, avec une constante diélectrique relative de ≈4). Ces propriétés déterminent ensemble l'impédance caractéristique de la trace. Un choix pratique pour les lignes à extrémité unique est 50 Ω[10] et 100 ohm pour le différentiel.

À cause de la faible impédance requise pour l'adaptation, les traces du circuit imprimé portant le signal, transportent beaucoup plus de courant que leurs homologues sur puce. Ce courant plus fort induit une diaphonie, principalement dans le mode magnétique ou inductif, là où on aurait eu une diaphonie en mode capacitif. Afin de contrer cette diaphonie, les concepteurs de circuits imprimés numériques doivent demeurer conscients non seulement du chemin prévu pour chaque signal, mais aussi du chemin de retour du courant du signal et ce, pour chaque signal. Le signal lui-même et le trajet de son courant de retour peuvent également générer de la diaphonie inductive. Des paires de traces différentielles aident à réduire ces effets.

Une troisième différence entre les connexions sur puce et puce à puce concerne la section transversale du conducteur du signal. Les conducteurs du circuit imprimé sont beaucoup plus grands, avec une largeur typique d'au moins 100 µm. Les traces du circuit imprimé ont une faible résistance en série (typiquement 0,1 Ω/cm) en courant continu. Cependant, la composante haute fréquence de l'impulsion est atténuée par une résistance supplémentaire due à l'effet de peau et à l'angle de perte diélectrique associée au matériau du circuit imprimé.

Le principal défi dépend souvent de la nature du projet : soit une application grand public dominée par le coût, soit une application d'infrastructure axée sur les performances[11]. Dans le premier cas, cela nécessite généralement une vérification approfondie après la conception à l'aide d'un simulateur électromagnétique (en) et dans le second, une optimisation de la conception à l'aide du logiciel SPICE et d'un simulateur de canal.

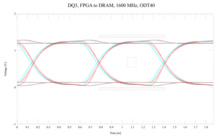

Topologie de routage

modifierLes niveaux de bruit sur une trace ou un réseau dépendent fortement de la topologie de routage sélectionnée. Dans une topologie point à point, le signal est acheminé directement de l'émetteur vers le récepteur. Cela s'applique entre autres dans PCIe, RapidIO, GbE, DDR2/DDR3/DDR4 DQ/DQS. Une topologie point à point pose moins de problèmes d'intégrité du signal, car les lignes T, qui sont une division bidirectionnelle d'une trace, n'introduisent pas de désadaptations d'impédance importantes.

Pour les interfaces où plusieurs composants reçoivent le même signal de la même ligne, comme dans les configurations avec fond de panier, on doit diviser la ligne à un certain endroit pour desservir tous les récepteurs. On doit s'attendre sur certains tronçons à des asymétries d'impédance. Les interfaces multi composants comprennent les interfaces LVDS, les bancs Commandes/Adresses des RAM DDR2/DDR3/DDR4, le RS485 et le bus CAN. Les deux principales topologies multi composants existantes sont l'arborescence et le fly-by.

Recherche des problèmes d'intégrité du signal

modifier- Effectuer une extraction de configuration pour obtenir les parasites associés à la configuration. Généralement, on extrait et on utilise les parasites correspondant au pire et au meilleur cas dans les simulations. En raison de la nature distribuée de nombreuses dégradations, on utilise la simulation électromagnétique[12] pour l'extraction.

- Si le circuit imprimé ou le boîtier existent déjà, le concepteur peut également mesurer la dégradation présentée par la connexion à l'aide d'un instrument de mesure à haute vitesse telle qu'un analyseur de réseau vectoriel. Par exemple, le groupe de travail IEEE P802.3ap utilise des paramètres S mesurés comme cas types[13] pour proposer des solutions au problème de l'Ethernet à 10 Gbit/s sur les fonds de panier.

- Une modélisation précise du bruit s'avère indispensable. Créer une liste des événements de bruit attendus, y compris les différents types de bruit, tels que le couplage et le transfert de charges. On peut utiliser les modèles IBIS (Input Output Buffer Information Specification) ou les modèles de circuits pour représenter les émetteurs et les récepteurs.

- Pour chaque événement de bruit, décider quels signaux d'entrée doivent être créés pour le circuit afin de produire l'événement de bruit.

- Créer une netlist SPICE (ou un autre simulateur de circuit) représentant l'excitation souhaitée.

- Exécuter SPICE et enregistrer les résultats.

- Analyser les résultats de la simulation et décider si une nouvelle conception est nécessaire. Pour analyser les résultats assez souvent, on génère un diagramme de l'œil et on calcule un budget de synchronisation. On peut trouver sur YouTube un exemple de vidéo sur la manière de générer un diagramme de l'œil : An Eye is Born .

Des outils EDA spécifiques[14] existent pour aider l'ingénieur à effectuer toutes ces étapes sur chaque signal d'une conception. Ces outils signalent les problèmes et vérifient que la conception est prête pour la fabrication. Pour sélectionner l'outil le mieux adapté à une tâche particulière, il faut tenir compte des caractéristiques de chacun, telles que la capacité (le nombre de nœuds ou d'éléments), les performances (vitesse de simulation), la précision (à quel point les modèles sont valides), la convergence (à quel point le solveur est valide), la capacité (non linéaire ou linéaire, dépendante ou indépendante de la fréquence, entre autres considérations) et la facilité d'utilisation.

Résolution des problèmes d'intégrité du signal

modifierUn concepteur de composants en circuits intégrés ou de circuits imprimés élimine les problèmes d'intégrité du signal grâce à plusieurs techniques.

- Placer un plan de référence solide adjacent aux traces de signal pour contrôler la diaphonie

- Contrôler l'espacement de la largeur de la trace par rapport au plan de référence pour créer une impédance de trace cohérente

- Utilisation des terminaisons adaptées (en)[15] pour contrôler la suroscillation

- Acheminer les traces perpendiculairement sur les couches adjacentes afin de réduire la diaphonie

- Augmenter l'espacement entre les traces afin de réduire la diaphonie

- Fournir des connexions de masse et d'alimentation suffisantes pour limiter le rebond au sol. Cette sous-discipline de l'intégrité du signal est parfois nommée intégrité d'alimentation

- Distribution d'énergie avec des couches planes solides pour limiter le bruit d'alimentation

- Ajout d'un filtre de préaccentuation à la cellule de commande de l'émetteur[16]

- Ajout d'un égaliseur à la cellule réceptrice

- Circuit d'horloge et de récupération de données amélioré avec un faible bruit de gigue/phase[17]

Chacun de ces correctifs peut entraîner d'autres problèmes qui devront être traités dans le cadre des flots de conception et de la fermeture de la conception.

Annexes

modifierBibliographie

modifier- Saverio Lerose, Intégrité de signal et compatibilité électromagnétique (CEM) des cartes électroniques, Techniques de l'ingénieur, (présentation en ligne)

- Fabien Ndagijimana, Intégrité du signal : Compatibilité électromagnétique dans les interconnexions haut débit, Londres, Ed. Iste, coll. « Traitement du signal et de l'image », , 176 p. (ISBN 9781784050245, EAN 9781784050245, lire en ligne)

- (en) Howard Johnson et Martin Graham, High-speed signal propagation : advanced black magic, Upper Saddle River, New Jersey, Prentice Hall PTR, , 806 p. (ISBN 0-13-084408-X, lire en ligne)

- (en) Eric Bogatin, Signal and Power Integrity : Simplified, Second Edition, Upper Saddle River, New Jersey, Prentice Hall, , 793 p. (ISBN 978-0-13-234979-6)

- (en) Stephen H. Hall, Garrett W. Hall et James A. McCall., High speed digital system design : a handbook of interconnect theory and design practices, New York, Wiley, , 347 p. (ISBN 0-471-36090-2)

- (en) William J. Dally et John W. Poulton., Digital systems engineering, Cambridge, Cambridge Univ. Press, (ISBN 0-521-59292-5)

- (en) Douglas Brooks, Signal integrity issues and printed circuit board design, Upper Saddle River, New Jersey, Prentice Hall PTR, , 418 p. (ISBN 0-13-141884-X, lire en ligne)

- (en) Geoff Lawday, David Ireland et Greg Edlund, A signal integrity engineer's companion : real-time test and measurement and design simulation, Upper Saddle River, New Jersey, Prentice Hall, , 504 p. (ISBN 0-13-186006-2)

- (en) Raj et A. Ege Engin., Power integrity modeling and design for semiconductors and systems, Upper Saddle River, New Jersey, Prentice Hall, (ISBN 978-0-13-615206-4)

- (en) Vikas Shukla, Signal integrity for PCB designers, The author, , 264 p. (ISBN 9780982136904, lire en ligne)

Liens externes

modifier- (en) Altera, « Basic Principles of Signal Integrity », (consulté le )

- (en) « Altera's Signal Integrity Center »,

- (en) « EEsof EDA »

- (en) Eric Bogatin, « Understanding signal integrity : signal integrity is becoming a more significant problem as clock frequency increases », (consulté le )

Articles connexes

modifierNotes et références

modifier- (en) Cet article est partiellement ou en totalité issu de l’article de Wikipédia en anglais intitulé « Signal integrity » (voir la liste des auteurs).

- On peut corriger certaines erreurs par le contrôle de redondance cyclique.

- Un phénomène associé à la commutation d'un transistor à effet de champ dans lequel la grille passe à un potentiel inférieur à la masse, causant une instabilité.

- Dans les installations électromécaniques, le rebond mécanique des contacts à la commutation, et le rebond de masse que cause l'inductance des bobines des relais, forçant le courant à continuer alors que le contact est ouvert.

- Traduction de Noise margin (en), Michel Fleutry, Dictionnaire encyclopédique d'électronique anglais-français, La maison du dictionnaire, (ISBN 2-85608-043-X), p. 565.

- traduction de « Latchup » selon Commission électrotechnique internationale, « Dispositifs à semiconducteurs et circuits intégrés : termes spécifiques aux circuits intégrés », dans IEC 60050 Vocabulaire électrotechnique international, (lire en ligne), p. 521-10-11.

- « verrouillage à l'état passant » selon Fleutry 1991, p. 433.

- Traduction de lane, Fleutry 1991, p. 428

- Shukla 2015.

- Louis Kossuth Scheffer; Luciano Lavagno; Grant Martin (eds), Electronic design automation for integrated circuits handbook, Boca Raton, Florida, CRC/Taylor & Francis, (ISBN 0-8493-3096-3)

- Johnson et Graham 2002.

- « Pratiques recommandées en conception numérique - Intégrité du signal », sur extron.fr, (consulté le ).

- (en) Michael S. Mahoney, « 31. Computer science : the search for a mathematical theory », dans John Krige & Dominique Pestre, Companion Encyclopedia to science in the twentieth century, (1re éd. 1997) (présentation en ligne), p. 253-274.

- (en)Ruckerbauer, « An Eye is Born » Gives an example video of construction of an eye pattern

- « Rule of Thumb #3 Signal speed on an interconnect », EDN (consulté le )

- "Signal Integrity: Problems and Solutions", Eric Bogatin, Bogatin Enterprises

- "Eight Hints for Debugging and Validating High-Speed Buses", Application Note 1382-10, Agilent Technologies

- « Why 50 Ohms? », Microwaves101 (consulté le )

- (en) Paul Rako, « Voices: Signal-integrity experts speak out: Two experts discuss signal-integrity challenges and their expectations for signal integrity », EDN, (lire en ligne [archive du ])

- (en) "Hurdle the multigigabit per second barrier"

- (en) IEEE P802.3ap Task Force Channel Models

- (en) Gary Breed, « High Speed Digital Design Benefits from Recent EDA Tools Development », High Frequency Electronics, , p. 52 (lire en ligne, consulté le ) :

« ...with continued increase in clock rates of digital circuits, the realms of RF and digital circuits are now more closely tied than ever before. »

- Commission électrotechnique internationale, « Lignes de transmission et guides d'ondes : Terminaisons et charges », dans IEC 60050 Vocabulaire électrotechnique international, (lire en ligne), p. 726-11-09

- « Using Pre-Emphasis and Equalization with Stratix GX », Altera

- "Using Clock Jitter Analysis to Reduce BER in Serial Data Applications", Application Note, literature number 5989-5718EN, Agilent Technologies